在計算機軟件技術服務與硬件系統設計中,時鐘源如同心臟,為整個系統提供穩定而有節奏的“脈搏”。而EMI時鐘源,正是這一核心組件中兼顧高性能與低電磁干擾(EMI)的關鍵技術。本文將為您解析什么是EMI時鐘源,并帶來其最新技術動態。

什么是EMI時鐘源?

EMI時鐘源,全稱為低電磁干擾時鐘源(Low-Electromagnetic Interference Clock Source),是一種專門設計用于減少工作時產生的電磁輻射的時鐘信號發生器。在計算機、通信設備、消費電子等各類電子系統中,時鐘電路產生的電磁噪聲可能干擾系統自身及其他附近設備的正常運行,導致數據錯誤、性能下降或合規測試失敗。EMI時鐘源通過優化時鐘信號的頻譜特性、采用展頻技術(SSC)或特殊濾波設計,將電磁能量分散到更寬的頻帶上,從而顯著降低峰值輻射強度,確保系統在復雜的電磁環境中穩定可靠。

EMI時鐘源的技術核心

- 展頻技術(Spread Spectrum Clocking, SSC):這是最常用的EMI抑制方法。它通過輕微且周期性地調制時鐘頻率(通常在±0.25%到±2%之間),將原本集中在單一頻率的電磁能量“攤薄”到一個窄帶范圍內,從而降低峰值輻射,滿足FCC、CE等電磁兼容性標準。

- 低抖動設計:在抑制EMI的必須保證時鐘信號的時序精度(低抖動),否則會影響高速接口(如PCIe, USB, SATA)和數據傳輸的可靠性。先進的EMI時鐘源實現了抑制干擾與保持信號完整性的平衡。

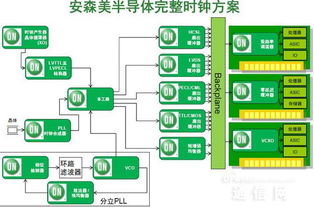

- 多輸出與可編程性:現代系統芯片(SoC)和FPGA需要多個不同頻率的時鐘。集成的EMI時鐘發生器可以提供多個低EMI輸出,并支持軟件配置,極大簡化了硬件設計。

最新技術報道與趨勢

隨著5G通信、人工智能、物聯網和汽車電子的飛速發展,對EMI時鐘源的性能要求日益嚴苛,其最新發展呈現出以下趨勢:

- 更高頻率與更低相位噪聲:為支持PCIe 5.0/6.0、DDR5等超高速接口,時鐘源的工作頻率不斷提升,同時對相位噪聲(抖動)的控制要求達到飛秒級。新一代產品在提供高達1GHz以上輸出頻率的保持了卓越的EMI抑制能力。

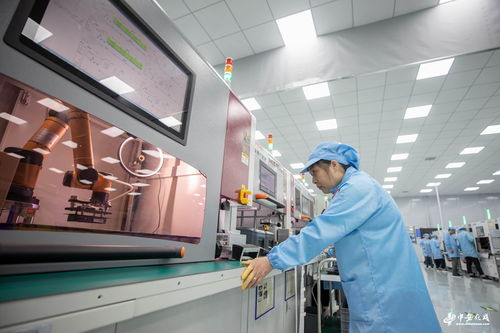

- 集成與系統級解決方案:時鐘源不再是一個獨立元件。它正被集成到更大的電源管理芯片(PMIC)或專用時鐘芯片組中,提供從核心CPU時鐘到外設接口時鐘的全套、同步的低EMI解決方案,助力設備小型化。

- 軟件定義與智能管理:在計算機軟件技術服務領域,時鐘的配置與管理變得愈發重要。通過I2C、SPI等總線,軟件可以動態調整時鐘頻率、啟用/禁用展頻功能,甚至根據系統負載和溫度進行實時優化,實現性能與功耗、EMI的最佳平衡。這為服務器、數據中心和邊緣計算設備提供了靈活的運維手段。

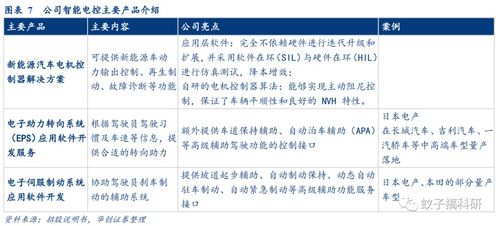

- 汽車級與工業級可靠性:自動駕駛和工業4.0推動了對AEC-Q100(汽車級)和寬溫、高可靠性時鐘源的需求。這些時鐘源能夠在極端環境和嚴苛的EMC標準下穩定工作。

- 主動EMI濾波技術:除了傳統的展頻技術,一些前沿設計開始采用有源濾波電路,實時監測并抵消特定頻段的噪聲,提供了更精準的EMI抑制效果。

對計算機軟件技術服務的意義

對于軟件技術服務工程師和系統架構師而言,理解EMI時鐘源至關重要:

- 系統穩定性保障:在驅動開發、系統部署和故障排查時,需知曉時鐘配置對系統穩定性的影響。不當的時鐘設置可能導致難以復現的間歇性錯誤。

- 性能調優工具:通過軟件接口對時鐘進行精細控制,成為系統性能調優(如超頻、節能)和滿足特定應用場景需求的有效手段。

- 預合規設計支持:在產品的軟件層面提前規劃時鐘管理策略,有助于硬件一次性通過EMC測試,縮短研發周期。

EMI時鐘源是連接高性能硬件與穩健軟件服務的基石技術之一。隨著技術演進,它正朝著更高性能、更智能集成、更緊密的軟硬件協同方向發展,持續為數字世界的可靠運行提供著清澈而穩定的“心跳”。